# HEWLETT-PACKARD JOURNAL

# **FEBRUARY 1984**

# HEWLETT PACKARD JOURNAL

Technical Information from the Laboratories of Hewlett-Packard Company

# **Contents:**

# FEBRUARY 1984 Volume 35 • Number 2

A New Series of High-Performance Real-Time Computers, by Marlu E. Allan, Nancy Schoendorf, Craig B. Chatterton, and Don M. Cross The HP 1000 A-Series provides 1 to 3 MIPS performance in a variety of configurations.

**An Adaptable 1-MIPS Real-Time Computer,** by David A. Fotland, Lee S. Moncton, and Leslie E. Neft The A700 offers user microprogramming, optional hardware floating-point, and optional error correcting memory.

**Designing a Low-Cost 3-MIPS Computer,** by Donald A. Williamson, Steven C. Steps, and Bruce A. Thompson It's done with pipelining, cache memory, and hardware floating-point, but not ECL.

Floating-Point Chip Set Speeds Real-Time Computer Operation, by William H. McAllister and John R. Carlson The add and multiply chips are fully combinational and produce a 64-bit result in 400 to 900 nanoseconds.

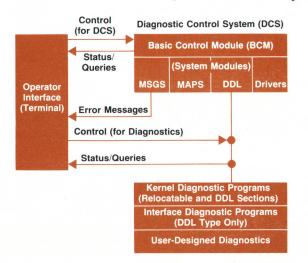

**Comprehensive, Friendly Diagnostics Aid A-Series Troubleshooting,** by Michael T. Winters and John F. Shelton An interpretive diagnostic design language makes it easy to generate diagnostics to fit the application.

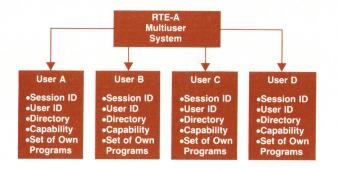

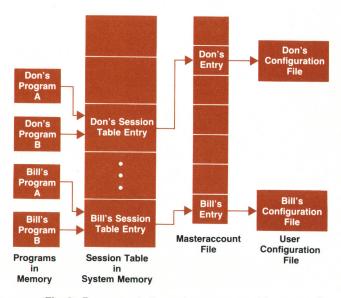

New Real-Time Executive Supports Large Programs and Multiple Users, by Douglas O. Hartman, Steven R. Kusmer, Elizabeth A. Clark, Douglas V. Larson, and Billy Chu Virtual code, code and data separation, and spooling are other features.

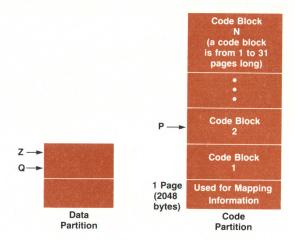

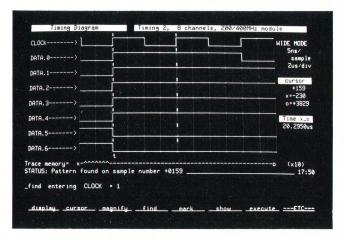

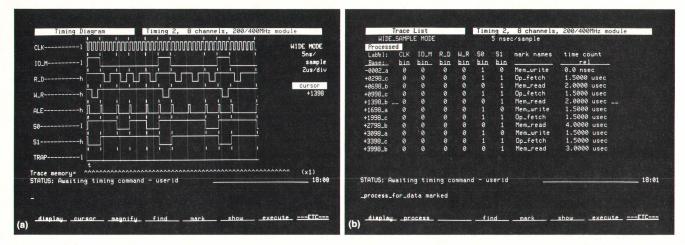

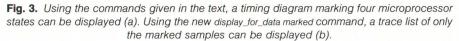

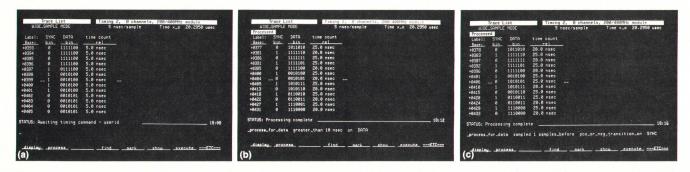

**New Software Increases Capabilities of Logic Timing Analyzer,** by David L. Neuder Marked events and postprocessing of trace data are a few of the capabilities added.

Authors

# In this Issue:

Real-time computers are designed to control or monitor real-world processes. These processes almost always involve other equipment, such as milling machines or semiconductor furnaces, and large numbers of sensors and activators. A real-time computer must keep up with the equipment around it. It must respond to interrupts quickly, it must transfer large amounts of data rapidly, and it must perform any necessary computations and data transfers efficiently, so that it is never overwhelmed by requests for its services. It must also be reliable, since a large amount of expensive material and equipment may depend on it.

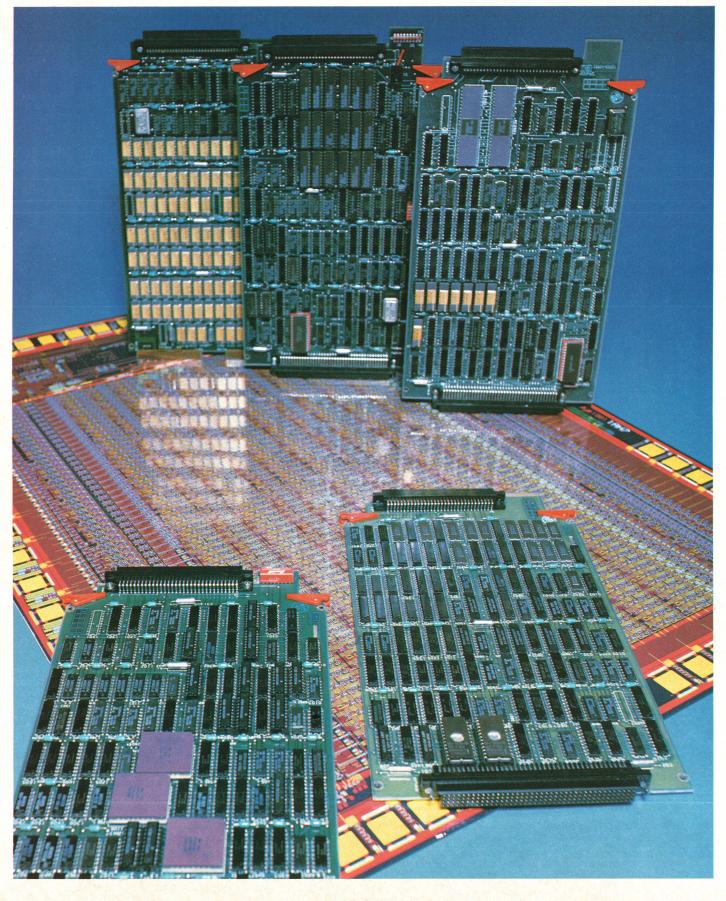

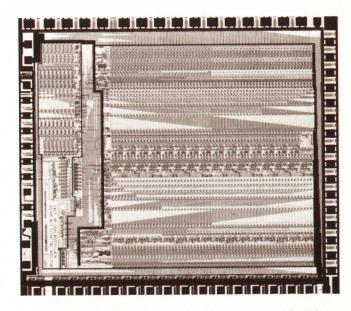

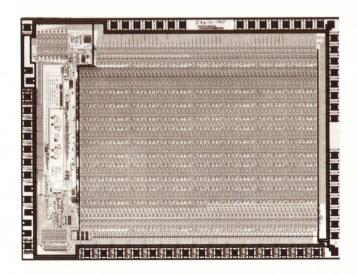

Hewlett-Packard's premier real-time computer family is the HP 1000 product line. In this issue you'll read about the new HP 1000 A-Series Computers, the highest-performance and most reliable HP 1000s developed so far, and about RTE-A, the latest version of the HP 1000's Real-Time Executive operating system. A-Series computers range in performance from the A600's one million instructions per second to the A900's three MIPS. To keep costs lower while achieving these high performance levels, the designers of the A-Series didn't go to a fast but expensive logic family like ECL (emitter coupled logic), choosing instead to rely on advanced architectures, special hardware, and clever ways to save microcycles. In the A900, they've provided a pipelined data path, a cache memory, and three special chips that add, multiply, and divide floating-point numbers. On this month's cover are the five boards of the A900 processor. The data path board (with the large square floating-point IC packages) and the cache memory board are in the foreground. In the background are the memory controller board, the sequencer board, and the memory board with its gold-covered RAMs. Under the boards is a color print of the mask set of the floating-point divide chip.

In designing microprogrammed processors like those in the A-Series and other microcomputer-based systems, logic analyzers and logic development systems are invaluable. Last March, we published a series of articles about the HP 64000 Logic Development System. One of its subsystems, the HP 64600S Logic Timing/Hardware Analyzer, has just been upgraded with some new software that gives the designer several sophisticated new ways to process and analyze timing data collected from a system under development. The story begins on page 32.

-R. P. Dolan

Editor, Richard P. Dolan

Associate Editor, Kenneth A. Shaw

Art Director, Photographer, Arvid A. Danielson

Illustrators, Nancy S. Vanderbloom, Susan E. Wright

Administrative Services, Typography, Anne S. LoPresti, Susan E. Wright

European Production Supervisor, Henk Van Lammeren

# A New Series of High-Performance Real-Time Computers

The HP 1000 A-Series consists of three compatible processors rated at up to 3 MIPS. They use a new Real-Time Executive operating system and are available in board, box, and system configurations.

# by Marlu E. Allan, Nancy Schoendorf, Craig B. Chatterton, and Don M. Cross

HE NEW HP 1000 A-SERIES family of computers is designed to provide solutions to specific real-time needs in manufacturing, automation, and other performance-critical environments. Implemented with stateof-the-art technology, the new computers offer major new capabilities to meet the challenging demands of OEMs, end users, and system designers.

The family consists of three compatible processors, the A600, A700, and A900. Each processor uses the new RTE-A operating system (RTE stands for Real-Time Executive), and identical compilers and subsystem products. Each computer employs the distributed-intelligence HP 1000 L-Series I/O system, which uses an I/O processor on each I/O card.

Available in board, box, and system configurations (see Fig. 1 and Table I), these processors offer configuration flexibility for OEMs and end users across a wide spectrum of applications. Ranging in performance from 1 to 3 million instructions per second, the A-Series family of computers offers very high performance at economical prices.

#### The A600 Processor

The A600 processor is the lowest-price member of the A-Series product line. Based on the 2901 microprocessor, the two-board CPU supports 128K bytes of memory, expandable to 4 megabytes. This processor combines microprogrammed instruction execution with hardware assist to achieve 1-million-operations-per-second performance. The A600 comes as a rack-mount computer and in numerous system configurations. It is best suited for dedicated applications, such as numerical control, energy management, and automated testing.

#### The A700 Processor

The A700 processor complements the A600 processor with additional capabilities. For computation-intensive applications, the A700 can be configured with an optional hardware floating-point processor or customized by user microprogramming. Optional error correcting (ECC) memory allows memory expansion to 2 megabytes in 512K-byte increments. Alternatively, the A700 can be configured with parity memory up to 4 megabytes in 1-megabyte increments. The A700 processor is available in a four-board processor configuration in addition to rack-mount and system offerings.

# The A900 Processor

The A900 processor is the highest-performance member of the A-Series product line. Using a 4K-byte cache memory, a pipelined data path, standard hardware floatingpoint chips, and microcoded scientific and vector instruction sets, the A900 can perform more than 3 million operations per second. Error correcting memory is standard in 768K-byte increments for a total memory capacity of 6 megabytes. A user-microprogramming package is available. The A900 is offered in rack-mount or system configurations.

# **RTE-A Operating System**

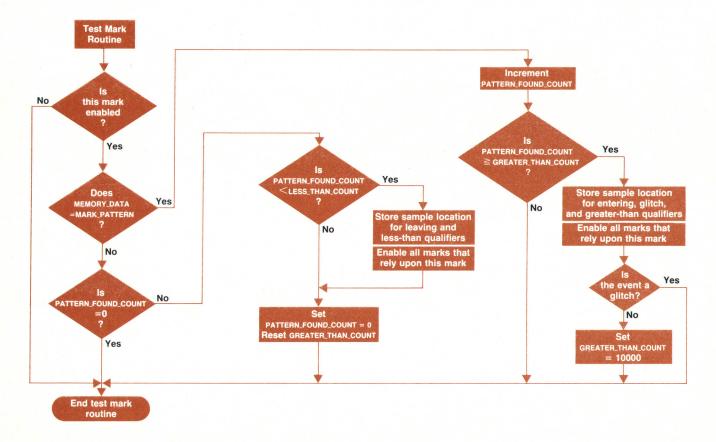

RTE-A is the real-time operating system for all three processors in the HP 1000 A-Series family. RTE-A evolved from previous members of the RTE family and is a product of some proven real-time features from past versions and some entirely new features. The main goals of the new features in RTE-A are to provide multiuser tools and to support large programs with large amounts of data. RTE-A

| HP                             | Table<br>1000 A-Series | -          |               |

|--------------------------------|------------------------|------------|---------------|

|                                | A900                   | A700       | A600          |

| System                         | 2199C/D,               | 2197C/D,   | 2196C/D,      |

|                                | 2439                   | 2437       | 2436          |

| Box                            | 2139A                  | 2137A      | 2136A         |

| Board                          |                        | 2107AK     | 2106AK        |

| Operating system               | RTE-A                  | RTE-A      | RTE-A         |

| Standard memory                | ECC                    | Parity     | Parity        |

| Optional memory                |                        | ECC        |               |

| Memory: Standard               | 768K bytes             | 256K bytes | 128K bytes    |

| Maximum                        | 6M bytes               | 4M bytes   | 4M bytes      |

| Memory cycle time              | 181 ns (eff)           | 500 ns     | 454 ns        |

| Hardware floating-point        | Standard               | Optional   |               |

| Operations/second              |                        |            |               |

| Base instruction set           | 3,000,000              | 1,000,000  | 1,000,000     |

| Floating-point                 | 500,000                | 204,000*   | 53,000        |

| Direct memory access           |                        |            |               |

| rate                           | 3.7M bytes/s           | 4M bytes/s | 4.27M bytes/s |

| User microprogramming          | Yes                    | Yes        | No            |

| FORTRAN77                      | Yes                    | Yes        | Yes           |

| Pascal/1000                    | Yes                    | Yes        | Yes           |

| BASIC/1000C                    | Yes                    | Yes        | Yes           |

| Graphics/1000-II               |                        |            |               |

| DGL & AGP                      | Yes                    | Yes        | Yes           |

| DSN/Distributed System         | Yes                    | Yes        | Yes           |

| *With hardware floating-point. |                        |            |               |

**Fig. 1.** *HP* 1000 *A*-Series Computers come in various configurations and have performance ratings ranging from 1 to 3 million instructions per second.

is implemented in a modular fashion so that one operating system can span the size and performance ranges of the entire A-Series. It is a configurable operating system and can be tailored by the user to fit any particular application.

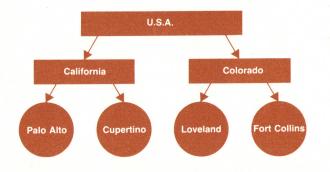

A major enhancement in RTE-A is the multiuser environment. A modern hierarchical file system allows logical grouping of files and protection of files. It also includes time stamping of files on creation, last access, and last update. This time stamping information is used to provide an incremental backup capability for the system. Another important feature of the enhanced file system is transparent access to files on other RTE nodes in a distributed system. This enhanced file system is used as a base for a multiuser environment. Logon and logoff utilities provide identification of users and their capabilities. This identification is used in conjunction with the protection mechanisms in the file system to identify and protect files belonging to individual users. The multiuser environment is completed with a command interpreter that has on-line help facilities and an outspooling utility for programmatic and interactive outspooling of files to devices or files.

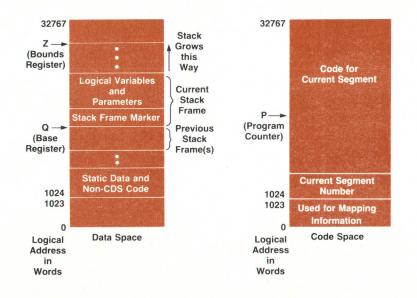

RTE-A has a number of features to support large programs and large amounts of data. Virtual memory for data is a scheme that allows users to access data in main memory and on disc as if it were all in main memory. EMA (extended memory area) is a special case of virtual memory for data. It provides faster access to data by allowing up to 2 megabytes of data in main memory. An EMA can be shared by multiple programs.

RTE-A takes advantage of new hardware features in the A-Series to provide separation of code and data for user programs. This allows transparent support of large programs (up to 7.75 megabytes of code) using a demand segment virtual memory scheme. It also allows multiple copies of the same program to share code.

#### **A-Series Performance**

The A-Series Computers were designed with excellent price/performance as an important goal. Their performance has been verified in benchmarks run against their predecessors and other currently competitive products.

Before discussing specific results, let's review how performance is typically measured. Computers are expected to perform a variety of tasks, from program development, to controlling and monitoring a milling machine, to assisting engineers in complex designs. In terms of performance, what's important to the people using these computers?

Some of the things often required are:

- Good throughput, or how much work can be done in a given amount of time. This may vary depending on what type of task is performed, e.g., floating-point computations, compiling programs, etc.

- Good response, or how fast the computer can respond to a certain input, such as an interrupt or a DMA transfer. An interrupt might be a terminal keyboard input, a sensor indicating a malfunction in a process, a satellite sending

data, etc.

Good utilization, or how effectively the resources are being used. If only part of the machine is used a significant amount of time, then the user may be paying for something unnecessary.

A-Series Computers are often used in real-time applications, where the computer must keep up with the equipment around it. Such environments require good performance in integer and floating-point operations, good interrupt response time and I/O transfer rates, and the ability to handle large amounts of data efficiently.

Benchmarks are standard programs used to compare the performance of one computer with that of another. One should be careful when selecting benchmarks to measure performance. Sometimes a particular benchmark may be biased in terms of what it's measuring, or may exploit a particular aspect of the computer that's not used much. The best benchmark is the application intended, but this is not always practical. The benchmarks discussed here are a small sample of the ones that have been run on the A-Series. The F-Series included in the results was previously the high-end HP 1000.<sup>1</sup>

The Whetstone benchmarks are industry standards that were written by the National Physical Laboratory of England. The programs are written in FORTRAN, and attempt to represent average program mixes. The two most common are the single- and double-precision Whetstones. These measure performance, including floating-point, in single and double precision, respectively (32-bit and 64-bit floating-point numbers). The performance results are shown in Table II, which indicates the execution times both in minutes and normalized relative to the A900. These times were measured on a quiescent system and are elapsed times. Note that the A700, A900, and F-series times include floating-point hardware while the A600 does floating-point operations in microcode. These benchmarks are often expressed in terms of "Whetstones per second." The execution times are for 10 million Whetstone instructions, so dividing this number by the execution times yields the column labeled KWIPS (thousands of Whetstones per second). The A900 KWIPS figures are better than those of many 32-bit "super minicomputers," even though the A900 is primarily a 16-bit computer.

In applications making little use of floating-point operations, integer performance is more important. A FORTRAN benchmark was developed to measure integer performance, and the results are shown in Table III. Here, single (16-bit) and double (32-bit) integer operations were measured. Normalized times are shown, referenced to the A900. Also, a MIPS figure is included, which is the number of millions of instructions executed per second. These figures are less than the base set instruction rates, since more complex instructions are required. In this example, the A900 does very well because of its optimized data paths and good 32-bit capabilities.

Many applications require the use of discs for storage and retrieval of data. Since discs are typically slower than the CPU, their effect must be taken into account. One such application is compiling programs. The A-Series supports a variety of compilers including a macroassembler, FOR-TRAN, and Pascal. While the speeds of these vary, the

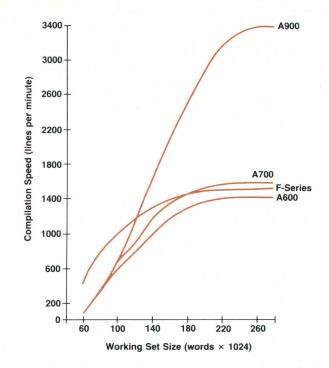

**Fig. 2.** Pascal compilation speeds for the HP 1000 A, E, and *F*-Series Computers.

relative performance is consistent. Compilation speeds for the Pascal compiler are shown in Fig. 2. These are in lines per minute and are measured in a quiescent system with a working set varying up to 270 pages (1024 words/page) using an HP 7925 Disc Drive. On the A900, only about 60% of the processor is used during a Pascal compilation. The remaining 40% is available for other activities.

The Pascal compiler is a VMA program, using the VMA (virtual memory area) capabilities of HP 1000 Computers. VMA allows a program to access up to 7.75M bytes of data, even though much of it may be on disc. The working set size is the amount of the data that can be in memory. The performance range is less here, since all of the A-series Computers use the same I/O system, and the disc time is now part of the execution time.

Interrupt response time is generally a good measure of how quickly a processor can respond to an external event. The data in Table IV is the elapsed time in microseconds from an interrupt until the system enters the appropriate driver. A driver is the piece of system software that communicates with a particular device or set of devices. Before entering the driver, the system must save certain state information and determine the appropriate action. Interrupt response time thus measures the operating system's performance as much as it measures the CPU's.

Even though the I/O systems are the same, much of the time is spent executing other instructions, and this results in the 3-to-1 range. An interrupt response time of 150  $\mu$ s is very good for a system with the functionality of RTE-A.

In selecting the right processor for a particular application, the type of performance necessary must be evaluated. The A-Series offers a range of CPU speeds from the A600 at 1 MIPS to the A900 at 3 MIPS. While the actual instruc-

| Table II                                             |

|------------------------------------------------------|

| Whetstone Performance                                |

| (Times are in minutes rounded to two decimal places) |

|                         | A900<br>time(rel)KWIPS | A700          | A600          | F-series      |

|-------------------------|------------------------|---------------|---------------|---------------|

| <b>Single Precision</b> | .12(1)1344             | .31 (2.6) 541 | .87 (7.3) 192 | .37 (3.1) 450 |

| <b>Double Precision</b> | .20(1)821              | .47 (2.4) 355 | 1.6 (8.0) 105 | .68 (3.4) 245 |

#### Table III **Integer Performance** (Times are relative to A900)

|                | time (MIPS) |           |           |           |

|----------------|-------------|-----------|-----------|-----------|

| Single Integer | 1.0 (2.3)   | 3.6 (.65) | 3.8 (.61) | 4.6 (.50) |

| Double Integer | 1.0 (1.9)   | 3.9 (.48) | 4.2 (.44) | 5.3 (.35) |

|                     | T<br>Interrupt I<br>(Times are i |     |     |  |

|---------------------|----------------------------------|-----|-----|--|

| Interrupt to Driver | 57                               | 142 | 146 |  |

tion execution rate will vary depending on the instruction mix, the range remains fairly consistent in many applications. Floating-point allows the A700 and A900 to excel, while heavier disc access compresses the range somewhat.

#### Reliability

HP customers have come to expect something extra in terms of reliability from HP products and the A-Series was designed with that in mind. Reliability, like quality, must be designed in. It cannot be added on later. One key to a reliable product is design margin, the attribute that enables a product to function properly over a wide range of environmental conditions and component variations.

To ensure sufficient design margin, a worst-case analysis was performed on each critical timing path in the A-Series CPUs. The A600 analysis was performed by hand while the A700 and A900 analyses were done using an HP-developed software package, which takes into account such parameters as power supply variation, output loading, temperature variation, and stripline characteristics of printed circuit boards to predict the operating margin of a digital circuit.

Before being made into a printed circuit board, each module of each of the A-Series Computers was analyzed by a group of engineers in a peer group design review. Each engineer in the review group was assigned the task of learning a portion of the module well enough to explain its detailed operation to the rest of the group. These review meetings have proved to be a very effective method of catching design errors early in a project.

After the printed circuit layout for each module was completed and digitized, the digitizer output was read by another HP-generated software package, which produced a list of all of the wires and connections on the board. The list was then checked against the schematic for the module as one final verification before boards were fabricated.

If components are operated at too high a temperature, even the most carefully designed circuit cannot deliver good long-term reliability. To ensure that each component would be operating well within its limits, thermocouples were used to look for potential hot spots that required additional cooling. The thermocouple data was used to calculate the junction temperature of each of the integrated circuits to ensure that no device was being overstressed.

As part of the development cycle, a number of typical A-Series system configurations were subjected to rigorous environmental tests designed to verify the integrity of the packaging, power supply, and processor electronics. Proper system operation was verified over a wide range of temperature, power line voltage and frequency, humidity, altitude, and vibration.

Care is also exercised during the manufacturing process to keep components from being damaged by electrostatic discharge (ESD). Often, a component will not be destroyed by ESD, but merely weakened, enabling it to pass production tests at the factory only to fail after a very few hours at the customer's site. To prevent this problem, we have implemented an extensive program to eliminate ESD damage to components during the manufacturing and testing process. The program includes antistatic mats, grounding straps for the workers, and antistatic conductive packaging for the transporting assemblies.

Mean time between failures (MTBF) calculations using RADC II methods predict the following MTBFs for the A-Series CPUs:

A600 (2156A) with 128K bytes of memory 10400 hours A700 (2137A) with 128K bytes of memory 7400 hours A900 (2139A) with 768K bytes of ECC memory

6100 hours

To date, field data on the 2156A and 2137A indicates that their MTBFs are actually 2 to 2.5 times better than the RADC prediction. At the time of this writing, the 2139A is too new and not enough field data is available on that product, but since it was designed using the same methodology and attention to detail that went into the 2156A and 2137A, there is every reason to believe that it too will give the high level of reliability that is expected from HP products.

#### Acknowledgments

The authors wish to thank all of the A-Series project members for their contributions in making the program successful. Their specific contributions are mentioned elsewhere in this issue. In addition, many people from other areas played important roles in the process of developing and releasing these products. Special thanks to Sara Dickinson and the A600 project team for their efforts, to Carl Synder for his assistance in managing the A-Series program, and to Nick Coping for his assistance during the development and system integration phases of RTE-A.

#### References

1. J. Cates, "F-Series Extends Computing Power of HP 1000 Computer Family," Hewlett-Packard Journal, Vol. 29, no. 14, October 1978.

2. RTE-A.1 Performance Brief, Hewlett-Packard Company, December 1982.

# An Adaptable 1-MIPS Real-Time Computer

by David A. Fotland, Lee S. Moncton, and Leslie E. Neft

HE A700 COMPUTER is the midrange processor of the A-Series Computer family. Priced between the A600 and the A900, the A700 provides flexibility that allows it to adapt to a customer's needs. The A700 can be purchased with or without hardware floating-point and with or without error correcting memory, and it can be customized through user microprogramming. It is designed to operate on the earlier HP 1000 L-Series backplane and thus it can use the dozens of I/O cards that have been developed since the advent of the L-Series.

The A700 was the first member of the A-Series product line, and its inherent flexibility made it the development processor of that product line. The first objective of the A700 was to overcome the address space limitation of the L-Series, while surpassing L-Series performance by a factor of 3. Another objective was to leverage the hundreds of engineer-years of effort found in the RTE family of operating systems, languages, and subsystems. The A700 was intended to provide all of the functionality of the HP 1000 E-Series and F-Series Computers, including similar performance and microprogrammability, at lower cost, using the improved L-Series I/O system and an improved method for supporting large programs.

The A700 was the first HP 1000 to make use of bit-slice technology, the first to incorporate the high-performance SOS floating-point chip set (see page 17), the first to implement the dynamic mapping system for large address space access, the pioneer and the development processor for large-program support provided by code and data separation hardware and the VC+ enhancement to the RTE-A operating system (see page 26), and the first HP 1000 to be easily user-microprogrammable through the use of the microparaphraser microprogramming language. The A700 with hardware floating-point has better performance than the HP 1000 F-Series, formerly the top of the line, at only sixty percent of the cost.

#### **New DMS Instructions**

Since the L-Series did not have memory mapping, the A700 was free to define a new improved set of dynamic mapping system instructions. The HP 1000 uses 15-bit logical addresses, so a program can directly address 32K words. A map is a set of 32 map registers which map the 32 1K-word pages of logical address space to 32 physical pages. For backward compatibility with the HP 1000 M.E. and F-Series Computers, the A-Series has a similar format for a set of map registers. The number of map sets is increased from 4 to 32 for more flexibility and the physical page number field is extended to allow 24-bit physical addresses. This allows the operating system to allocate one DMS map to each I/O interface for increased I/O throughput. In addition, the operating system can use a separate DMS map for system available memory. The user program can be allocated two maps, one for code and one for data.

The DMS instruction set includes instructions for loading and storing maps and a new set of cross-map instructions that allow access to memory through three maps, the current execute map and two others called data1 and data2. The cross-map instructions include load, store, and move words.

#### **CDS Instructions**

The biggest architectural change was the introduction of code and data separation. Separation of code and data allows programs with large code to be handled easily and transparently without using overlays. It also provides better protection, recursion, and reentrancy. It allows code to be shared between several processes to conserve main memory. CDS was recognized early as being a desirable goal. The problem was to provide it without a major change in the existing instruction set, which would require a lot of extra hardware. The old instruction set is faithfully executed for backward compatibility. Minimal changes from the old instruction set also mean minimal changes to the existing compilers.

#### **ECC Memory**

No matter how good the design or how reliable the parts used, machines will fail from time to time. The single part in the A700 that contributes most to the failure rate is the dynamic RAM chip used in the memory. This is because these parts have a high soft failure rate compared to other logic parts and because there are many more RAM chips in the machine than any other kind of chip. An A700 with 4M bytes of memory contains 544 64K-bit dynamic RAM chips.

Error correcting memory provides higher reliability for those customers who need it by correcting single-bit errors and detecting double-bit errors. Soft errors are the most common failure of memory systems. In systems with over 512K bytes of memory the soft error rate is about one per year. Customers who need higher reliability than this can use error correcting memory.

Error correcting memory is easy to use on the A700 because it uses the same memory controller and has the same performance as parity memory. A customer can upgrade to error correction without throwing out the current controller. Error correcting and parity memory can be mixed in the same system. For example, one might want to protect the operating system and some critical applications from single-bit errors, and use less-expensive parity memory for the rest of the system.

If there are no errors, the error correcting memory runs at the same speed as parity memory. When a single-bit error is detected, the system is frozen for 200 ns while the data is corrected, and is then allowed to continue with good data.

A Hamming code is used to detect and correct memory

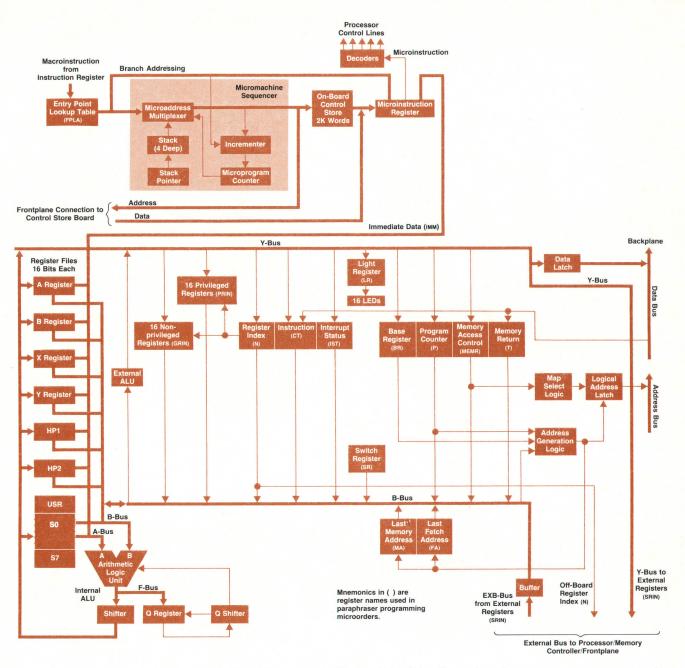

Fig. 1. Block diagram of the A700 processor. The regularity of data flow makes microprogramming easier.

errors in the A700. With the addition of 6 bits per 16-bit word all single-bit errors are correctable and all double-bit errors are detectable. Whenever the memory is read the parity bits are combined with the data to provide a 6-bit syndrome, which identifies the type of error and the bit number if it is a single-bit error. This syndrome is stored in an error logging RAM in the memory controller. There is one syndrome location in the RAM for each row of 64K RAM chips. By reading the error logging RAM, it is possible to determine the last chip that had an error in each row of RAMs. This information can be used to identify failed chips before they cause a problem in the system.

#### Performance and Ease of Microprogramming

The two major objectives in the design of the A700 micromachine were to provide fast execution of the HP 1000 instruction set, and to allow user microprogramming, which can give a substantial boost in performance to many customer applications. To accomplish these objectives, we designed an architecture that is simple and straightforward, a microinstruction set that is flexible and provides a lot of capability, and tools that aid microcode development.

We chose to base the micromachine on the 2900 bit-slice processor family, specifically the 2903 bit-slice processor and the 2911 bit-slice sequencer. These parts provide many intrinsic features, yet allow us to use our own microarchitecture. We use the 2903's numerous arithmetic and logical operations, but use our own instruction set for accessing them.

#### The Microarchitecture

The key features of the microarchitecture are capability and regularity. The capability allows fast performance; the regularity makes it easy to microprogram.

To optimize performance for the A700 instruction set, we used profile data which told us how often each instruction or class of instructions was executed for different types of programs. For those instructions executed most often, we provide special hardware to shorten their execution times. We avoided the common pitfall of making other instructions inordinately slow to optimize the most heavily used instructions. Even an instruction that occurs only 1% of the time can impact performance if it's extremely slow. However, it is not practical to provide special hardware for all instructions. Since much of our instruction execution time is spent in decoding the instruction (that is, determining what the instruction is), we designed the micromachine to decode all instructions quickly. By increasing the performance for instructions that had slow execution times in previous HP 1000s, we allow more flexibility in the design of applications that use assembly language (such as compilers).

Optimizing the design for user microprogramming was more difficult. To accomplish this, we looked at the types of functions that were likely to be microcoded (for example, computation and bit manipulation) and provided sufficient hardware to support these types of operations. Many of the operations were all ready provided in the 2903; we needed only to design the hooks to access them.

A block diagram of the processor is shown in Fig. 1. The regularity of the flow of data through the machine is one of the features that contributes to the ease of microprogramming. At the start of a cycle, data is enabled from the appropriate registers onto the operand buses: the A-bus and the B-bus. In one cycle, data is input to the ALU and passed to a shifter. The resulting data is available on the Y-bus at the end of the cycle. The Y-bus result can then be loaded into a register or written to main memory. In the following cycle, conditions generated by the operation just described, such as carry out of the ALU, can be tested. The user does not need to learn complex rules for the relationship between buses, registers, and conditions, since they are the same throughout the machine. Registers are updated at the end of the cycle and are available as operands for the next cycle. The conditions that are tested are the conditions that were generated during the previous cycle.

The flow of control in the micromachine is similar to high-level languages such as BASIC or FORTRAN. Jump (goto) or jump to subroutine (call) instructions are used to transfer control to nonsequential locations in micromemory.

The key to the flexibility and performance of the A700 micromachine is the microinstruction set (called microoperations) and the microinstruction format. The width of the microinstruction word was an important design decision. A longer microword means more operations can be done in one microinstruction. This does not directly translate into an increase in performance, since certain operations need to be done sequentially, such as adding two numbers and then checking for overflow. We were also developing writable control store (WCS) and PROM control store (PCS), and a shorter microword makes these boards less expensive and allows more words of micromemory on each control store board. By careful encoding and overlapping of fields, we were able to use a 32-bit microinstruction word that allows several operations to be done in one cycle (see Fig. 2). Fewer microoperations are available in a jump instruction than in an instruction that does not use a jump. However, in every microinstruction, one can perform an arithmetic or logical operation with the contents of two registers and store the result in any register in the machine. For example, one can add the contents of two registers, perform a shift on the result, and then jump to another location in micromemory, all in one cycle. To test this design decision, most of the base instruction set was microcoded before the processor hardware design was solidified.

The decoding scheme for microinstructions ensures that no combination of codable operations can damage the processor hardware (such as enabling two registers onto the same bus). Any other illegal combination of operations is detected by the microparaphraser. Thus the microprogrammer need only remember the basic relationships for data in the machine, the microinstruction formats, and a few special rules concerning interaction with main memory, I/O, and the mapping system.

A hardware timeout feature provides some protection

| Bit                | 31 30                          | 29 28                   | 27 26 25 24 23 | 22 21 20 19 18       | 17 16 15 14 | 13 12 11 10 | 98765 | 4 3 2 1 0 |

|--------------------|--------------------------------|-------------------------|----------------|----------------------|-------------|-------------|-------|-----------|

| Word<br>Type<br>1  | c                              | P1                      | ABUS           | SP0                  | SP2         | ALU         | BBUS  | STOR      |

| Word<br>Type<br>2  | c                              | )P2                     | ABUS           | SP0                  | CNDX        | ALU         | BBUS  | STOR      |

| Word<br>Type<br>3  | OF                             | •3                      | ADRS           | SP1                  | CNDX        | ALU         | BBUS  | STOR      |

| Word<br>Type<br>4  | 0                              | P4                      | ADRS           | SP1                  | SP2         | ALU         | BBUS  | STOR      |

| Word<br>Type<br>5  | OP5 ADRL (Long Branch Address) |                         |                | ALU                  | BBUS        | STOR        |       |           |

| Word<br>Type<br>6  | OP6                            | P6 DAT (Immediate Data) |                | ALU                  | BBUS        | STOR        |       |           |

| Word<br>Type<br>1S | c                              | )P1                     | ABUS           | ALUS*                | SP2         | SPEC        | BBUS  | STOR      |

| Word<br>Type<br>2S | c                              | P2                      | ABUS           | ALUS*                | CNDX        | SPEC        | BBUS  | STOR      |

| Word<br>Type<br>3S | o                              | <b>9</b> 3              | ADRS           | ALUS*                | CNDX        | SPEC        | BBUS  | STOR      |

| Word<br>Type<br>4S | о                              | P4                      | ADRS           | ALUS*                | SP2         | SPEC        | BBUS  | STOR      |

| Word<br>Type<br>5S | o                              | P5                      | (Long Ju       | ADRL<br>Imp Table Ad | ddress)     | SPEC        | BBUS  | STOR      |

\*Special microorder in ALUS field when ALU field is coded SPEC.

Fig. 2. A700 microinstruction formats.

from errant user microprograms. This protects the system from a user microprogram's hanging and not allowing system interrupts. If a system interrupt goes unserviced for more than 10 ms, then the microprogram is aborted and control is returned to the operating system.

# The Microparaphraser

One of the most important tools for the development of microcode on the A700 is the microparaphraser, MPARA. The microparaphraser was originally developed for the A700 and later adapted for the A900. All of the base instruction set, the floating-point instructions, and the microcode diagnostics were written using MPARA.

MPARA allows the user to write microcode in free format, Pascal-like constructs. It then translates them into microcode. The following example shows a microroutine that finds the maximum of two numbers.

| \$origin 0x3000\$                                      | *Start routine at 3000 hex.                                                              |

|--------------------------------------------------------|------------------------------------------------------------------------------------------|

| MAX:                                                   | A = arg1, B = arg2.                                                                      |

| s1:=a-b;                                               | *Compare arguments.                                                                      |

| if alov then goto ChangeSense;                         | *If arithmetic overflow then                                                             |

|                                                        | * switch sense of compare.                                                               |

| if y15 then stor,                                      | *If result was negative, then                                                            |

| a:=b;                                                  | * return arg2 (else arg1).                                                               |

| rtn;                                                   | *Return, max is in A.                                                                    |

| ChangeSense:                                           | *                                                                                        |

| if not y15 then stor,                                  | *If result was positive then                                                             |

| a:=b;                                                  | * return arg2 (else arg1).                                                               |

| rtn;                                                   | *Return, max is in A.                                                                    |

| rtn;<br>ChangeSense:<br>if not y15 then stor,<br>a:=b; | *Return, max is in A.<br>*<br>*If result was positive then<br>* return arg2 (else arg1). |

A phrase can be an arithmetic expression, such as:

$s_{1}:=a-b$

or a conditional operation:

if alov then goto ChangeSense or an individual microorder:

#### rtn

Phrases, which are delimited by commas, can be strung together in any order as long as they represent a legal microinstruction. A sentence is a complete microinstruction and is terminated by a semicolon. This type of format makes microcode easy to read and write and also allows plenty of room for comments (especially important for microprogramming).

#### Writable and PROM Control Store

Two types of user control store boards were designed to facilitate user microprogramming and to aid the design team in the development of the A700 processor. The PROM control store board (PCS) provides inexpensive storage for up to 8K of microcode. The writable control store board (WCS) allows microcode to be downloaded and altered dynamically during the debugging process.

Since the control store PROMs used in the A700 were initially expensive and not reprogrammable, it was not practical to change the base set PROMs on our breadboards whenever bugs were found during development. Therefore, we made use of a special feature of the A700 processor which allows us to overlay the base instruction set on the processor board with the microcode on the WCS board. Using this "mindswap" feature, we could download from the operating system the latest revision of microcode to the WCS, enable it, and continue to run in the operating system with the new microcode.

# Hardware Floating-Point Board

The hardware floating-point board for the A700 Computer is really two boards in one. A portion of the board is designed to be a PROM control store board that can hold 4K words of microcode PROM. The first 2K is used to hold the microcode that executes the floating-point-dependent instructions in the HP 1000 instruction set, that is, singleand double-precision floating-point, the scientific instruction set (SIS), and the vector instruction set (VIS). The second 2K is available for user-microcoded routines.

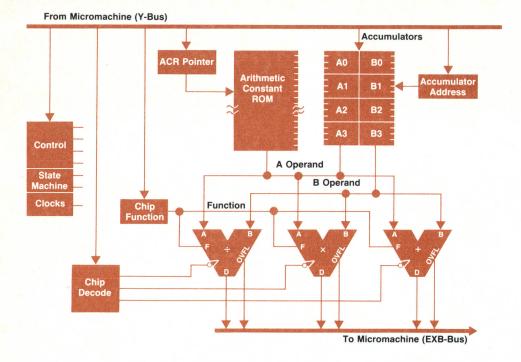

The main area of the board contains the floating-point hardware, which is used during the execution of floatingpoint instructions. This portion of the board is designed around the computational power of three CMOS/SOS floating-point chips (see page 17). These chips are designed specifically to perform HP 1000 integer and floating-point arithmetic.

The design of the floating-point board evolved through a number of iterations. These iterations required designing a preliminary version of the hardware, then writing the microcode for the floating-point, SIS, and VIS instructions using the features in that version of the hardware. After determining the execution time of the instructions and evaluating the good and bad features offered by that particular revision of the hardware, another pass at the hardware was made. This cycle was repeated until all the hardware capabilities needed to optimize the execution of the instructions were included in the design.

One of the more significant improvements in the design of the hardware was the addition of an on-board arithmetic constant ROM (ACR), which contains single- and doubleprecision floating-point constants. The ACR has over 100 constants which are used during the execution of the SIS instructions and for the self-test diagnostics. The ACR is accessed indirectly through an address pointer which is automatically incremented after each use, allowing the address pointer to be set to the front of a list of constants which are to be required in a known order. The main advantage of using the ACR is in eliminating the overhead required to pass fixed-value operands (e.g.,  $\pi$ ,  $\pi/4$ , ln2, 1/2, etc.) from the micromachine to the floating-point board. This savings is most significant in the evaluation of the SIS instructions where many constants are required in the polynomial approximation of the functions. (The evaluation of an arctangent can require up to seven constants.)

Another important feature is the set of four on-board accumulators, each capable of holding a single-precision (32-bit) or double-precision (64-bit) floating-point number. These accumulators eliminate the necessity of repeatedly passing the same floating-point number to the board when it is required more than once during the evaluation of an expression such as (x + y)/(x - y). The accumulators also increase performance by temporarily saving the intermediate results of a polynomial expression. The ability to save intermediate results on-board instead of unloading and later reloading the value significantly reduces the execution time of the SIS and VIS instructions.

Another feature included in the design of the floating-

**Fig. 3.** Internal data paths on the A700 hardware floating-point board.

point board is the ability to clock operands into the floatingpoint chips at twice the micromachine clock frequency. Because the input clock rate of the floating-point chips is twice the speed of the processor microcycle time, operations that do not require operands from the micromachine can clock their operands into the chips twice per microcycle. All transfers between the floating-point chips and the accumulators or ACR can be performed at twice the microcycle rate. This reduces the time spent in transferring the operands of intermediate results to the chips, and results in faster execution times.

To make the addition of the optional floating-point board to an A700 system easier, the floating-point microcode will overlay the portion of the microcode on the processor card that decodes floating-point-dependent macroinstructions. The floating-point board can then intercept and redirect the execution of the floating-point instructions to the microcoded routines contained on the floating-point board. Thus no changes need be made to the A700 base set microcode when the hardware floating-point board is added to the system, making customer upgrades simpler.

Fig. 3 shows a block diagram of the internal data paths on the floating-point board. Surrounding the three math chips are state machines, control logic, four accumulators, the ACR, and clocking circuitry. The hardware floatingpoint board is designed to be an optional coprocessor board for the A700 CPU. To the A700 micromachine, the floatingpoint board looks like four 16-bit registers. These four registers are readable and writable by the micromachine and appear as four locations in an external register file that are dedicated specifically for use with the floating-point board.

To use the floating-point board, a control word is first passed to one of the four dedicated registers. This control word contains such information as which chip to use, what operation to perform with that chip, where the operands are to come from (an accumulator, the ACR, or the micromachine), and where the result is to be stored. Once a control word is passed to the floating-point board, the necessary operands are then passed to the board through the dedicated register locations.

As pairs of operands of equal significance are available on the floating-point board, the control logic clocks that pair of operands into the selected floating-point chip. When all operands have been clocked into the chip and the required propagation delay has passed, the results of the operation are available to be read by the micromachine from one of the dedicated register locations. An overflow/ underflow signal is also available to the micromachine at one of the registers.

The microcode written for the floating-point board takes full advantage of the independence of the micromachine and the floating-point board. For example, during the time when an operation is being performed by the floating-point board, the micromachine can be resolving the indirect addresses for the result, fetching the next operand from memory, or doing arithmetic/logical operations of its own. This independence is used to full advantage during the execution of the VIS instructions. Each vector instruction was written to minimize the time to compute one element of the vector. This microcode generally has six operations to perform for each element of the vector:

- Execute the required floating-point operation

- Fetch the next operands from memory

- Return the results from the previous computation to memory

- Update all memory address pointers by the correct increment

- Check the loop count for the end of the instruction

- Check for system interrupts.

For each VIS instruction an inner loop was written that minimizes the time required to do this work. Because this code is optimized for execution speed and large memory bandwidth rather than ease of entry and exit, it is necessary to precede this code by a section of front-end code that synchronizes with the inner-loop code. The results of this work enable the VIS instructions to execute very close to memory speed for single-precision operations, and at memory speed for double-precision operations. This yields an improvement of  $1\frac{1}{2}$  to 3 times compared to the execution speeds on the HP 1000 F-Series Computer.

#### Acknowledgments

The authors wish to acknowledge the other members of the design team: Carolyn Guidry, Steve Kusmer, Earl Kieser, Tom Harms, and Bill Chesk, and especially our project manager Don Cross for his guidance and support. We'd like to thank our production engineer Chris Malachowsky and our product manager Scott Spielman for believing in us. Wayne Chin, Colleen Obergfell, and Dan Shewey also contributed to the success of the project.

# **Designing a Low-Cost 3-MIPS Computer**

by Donald A. Williamson, Steven C. Steps, and Bruce A. Thompson

HE A900 COMPUTER provides approximately three times the performance of any previous HP 1000 Computer, while maintaining full software compatibility with the other HP 1000 A-Series Computers. The cost of the A900 is noticeably lower than that of many computers of similar performance, giving it an excellent price/performance ratio. To achieve this price/performance ratio, the performance was optimized, but not by adding a lot of additional parts and complexity.

To increase the performance of a computer, the amount of work done in each machine cycle can be increased and the cycle time can be decreased. This can be accomplished by widening all of the paths to 32 or 64 bits and using a very fast technology such as emitter-coupled logic (ECL). This approach was not used in the A900 because it leads to a very high-cost computer. Instead, care was taken to add cost only where it was justified by a significant performance gain, and to minimize cost elsewhere.

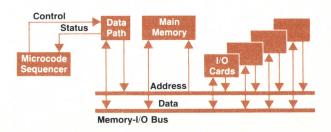

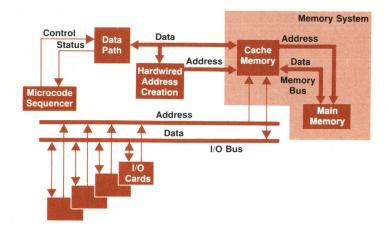

Although the A900 is completely software compatible with the other members of the A-Series, it has a somewhat different hardware structure. Fig. 1 shows a basic block diagram for both the A600 and A700 Computers, while Fig. 2 shows the basic block diagram for the A900. All three machines are microprogrammed and therefore have data paths that are controlled by a microcode sequencer. The A600 and A700 have a common memory-I/O bus used by both the CPU and the I/O system to access memory. The I/O bus in the A900 is electrically and mechanically the same bus as the memory-I/O bus in the A600 and A700. However, the A900 does not fetch instructions or data across this bus. The CPU uses the bus only to communicate with the I/O system. This structure helps achieve the main goal for the A900: high performance without the normally associated high price.

# Sequencer

The A900 is a microprogrammed computer. This means that each machine language instruction (macroinstruction) is emulated by a sequence of microinstructions. The format of the macroinstructions is fixed by compatibility with other HP 1000 Computers, but the format of the microinstructions is tailored to the hardware used to implement the A900.

Each microinstruction is 48 bits wide, allowing several operations to be specified in parallel. For instance, a conditional jump, an ALU operation, and a memory operation can all be coded in a single microinstruction. Thus the microprogrammer can test a condition, perform a calculation, and start reading the next operand, all simultaneously.

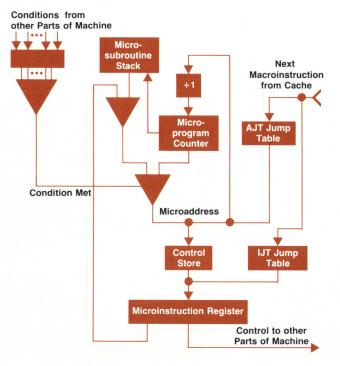

The microcode sequencer controls the sequence of microinstructions that are used to emulate each macroinstruction. A block diagram of the sequencer is shown in Fig. 3.

The sequencer selects a microaddress from the microprogram counter, the microsubroutine stack, or a field of the current microinstruction. The control store takes this address and generates a microinstruction which is loaded into the microinstruction register at the end of the microcycle. Usually, one of the critical timing paths in a microprogrammed machine is the decision point between a conditional branch and sequential execution. In the A900, the "condition met" signal controls a multiplexer at the output of the address selection logic. Thus the signal can arrive later in the cycle without becoming a critical timing path. This helps in reducing the cycle time of the A900 micromachine to 133 ns.

Each time a new macroinstruction is fetched, the se-

**Fig. 1.** A basic block diagram for the A600 and A700 Computers, showing the common memory-I/O bus.

**Fig. 2.** A basic block diagram for the A900 Computer, showing the separate memory and I/O buses.

quencer must determine the sequence of microinstructions needed to emulate it. Traditionally this is done by sending the macroinstruction to a jump table (AJT) which produces the address of the first microinstruction of the emulation sequence. Since this address must then be sent to control store to produce the actual microinstruction, the decoding process takes two entire cycles. The A900 adds another type of jump table (IJT) which receives the macroinstruction and produces a microinstruction instead of a microaddress. The IJT is built with programmable logic arrays (PLAs), and can produce microinstructions for the most common macroinstructions. While the IJT is guessing the first microinstruction of the emulation sequence, the AJT is looking up the address of the second microinstruction. While the first microinstruction is executing, the control store is looking up the second microinstruction. The result is that it takes only one cycle instead of two to determine

**Fig. 3.** The sequencer controls the sequence of microinstructions to emulate each macroinstruction.

the first microinstruction of the sequence. This is a significant savings, since many important macroinstructions take only two cycles to execute.

# **Pipelined Data Path**

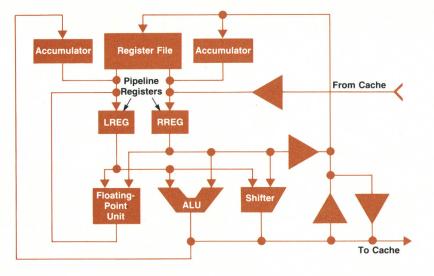

The data path is where much of the data manipulation required by the HP 1000 instruction set is done. A block diagram of the A900 data path is shown in Fig. 4. Operands from the register file, cache memory, or other parts of the machine are operated on by the ALU, the shifter, or the floating-point unit, and the result is stored in the register file, the cache, or some other machine register. Accessing the operands, performing the operation, and storing the result take longer than the 133 ns available in an A900 microcycle. Therefore, the data path is split into two pieces by a pair of pipeline registers.

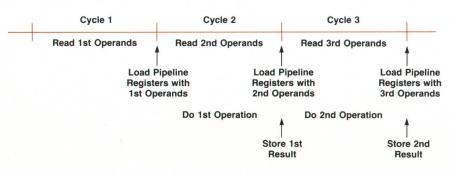

In the first cycle of a microinstruction, the operands are read and loaded into the pipeline registers. During the second cycle, the operation is performed using the values in the pipeline registers, and the result is stored. During this second cycle, the operands for the next microinstruction are being read. Even though it takes two cycles to complete a microinstruction, the parallelism allowed by the pipeline registers lets a new microinstruction start every cycle (see Fig. 5).

A side effect is that the result of a microinstruction started in cycle 1 is not stored until the end of cycle 2 and therefore cannot be used until cycle 3. The register file is paralleled by a pair of latches which can be used as accumulators. The latches become transparent if they are written at the same time that they are read. The result from a cycle 1 microinstruction can be written into one of the pipeline registers at the end of cycle 2 by storing it to an accumulator. In other words, if a result is stored to one of the accumulators it can be used immediately instead of one cycle later.

The data path is designed to maximize the amount of work that can be done by a single microinstruction. For instance, the register file is double-ported, allowing access to two operands at a time. The shifter can logically shift the 32 bits of data in the pipeline registers by 0 to 15 bits and produce a 16-bit result. Using this barrel shifter, any type of shift—arithmetic, logical, or circular—can be accomplished in a small number of cycles.

There are actually two independent paths within the

Fig. 4. The A900 data path. The two pipeline registers make it possible to start an operation while the preceding operation is still in progress. The accumulators make it possible to use the result of a microcycle immediately instead of one microcycle later.

data path. One of these is the path from the pipeline registers, through the ALU or shifter, and out to the cache or other register. The other is a path from the right pipeline register through a buffer to the register file. The paths are often interconnected by a bidirectional buffer pair. This allows simple operations such as storing the ALU output in the register file or passing the right-side operand to the cache. The paths can also be used independently, allowing two data transfers in a single cycle. For example, data from the cache can be passed to the register file using the right pipeline register, while data from the register file is sent to the cache via the left pipeline register and the shifter.

The floating-point unit dramatically reduces the number of cycles needed to perform floating-point operations. It uses the three LSI floating-point chips described in another article in this issue. Because the chips are tightly coupled into the data path, the 32 bits of data from the pipeline registers can be loaded into the chips each cycle. After a full set of operands is loaded, the chips produce the result, which can be unloaded via one of the pipeline registers several cycles later. The chips are also used to perform integer multiplication and division.

#### **Memory System**

The memory system includes three pieces. The first piece is the address creation logic. This logic generates the appropriate addresses for the cache, which might be used for fetching an instruction or reading the data needed for an instruction. The second piece is the cache memory. A cache memory is a very high-speed memory which keeps only a subset of main memory. The goal of a cache memory is that of any memory hierarchy: achieve performance close to that of the fastest memory (cache memory, in this case) with a cost closest to that of the slowest memory (main memory, in this case). The third piece of the memory system is the main memory itself.

One of the performance-critical parts of most computers is the path from instruction fetch to operand ready. This includes the decoding of the instruction, the extraction and merging of the appropriate fields, and the starting of the memory request. Typically, this is done by the micromachine using the main ALU. However, in the A900, almost all of this is done in hardware.

HP 1000 instructions that reference memory can be of two types. The memory reference group (MRG) instructions are the most commonly executed instructions in the HP 1000 instruction set. These instructions have a four-bit opcode, a 10-bit offset, a zero/current page bit, and a direct/indirect bit. The other type of memory reference instructions has a 16-bit opcode followed by a 15-bit address with a direct/indirect bit.

If the instruction is of the first type (MRG), the A900 hardware creates the appropriate address from the current program counter page value and the offset from the current instruction. A memory reference with this address is then started by the hardware. If the address is indirect, the address creation hardware can freeze the CPU until a direct address is read, since multiple levels of indirect addressing are allowed. If the instruction is of the non-MRG type, then the address creation hardware increments the program counter and starts a memory reference.

By the time the microcode sequencer can vector to the

**Fig. 5.** Timing in the pipelined A900 Computer. Although it takes two microcycles to complete a microinstruction, a new microinstruction is started every microcycle. correct microcode for the instruction, the memory operand data can be ready. This allows for a much shorter sequence of microinstructions for each machine language instruction. In fact, an instruction whose operand is another instruction (e.g., the jump instruction, JMP) can be executed in just one microcycle without the added cost and complexity of machine language instruction pipelining.

#### **Cache Memory**

The cache memory of the A900 has a data access time of 65 ns and a cycle time of 133 ns. This allows a memory reference every microcycle, thus allowing the computer to get more done per cycle. Also, since the access time of the cache is many times faster than that of main memory, the processor cycle time can be much shorter than that of a noncache system.

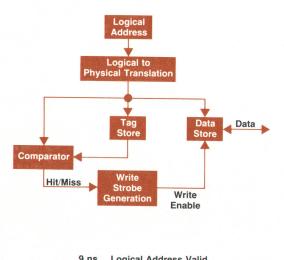

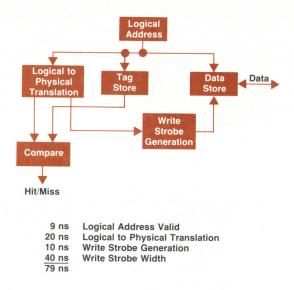

A normal cache structure is shown in Fig. 6. A cache write cycle cannot begin until the appropriate address is known to be in the cache. This means the minimum cycle time for a cache write is the time for valid address, plus the time to translate logical to physical address, plus the time to access the tag RAM, plus the time to compare the tag address to the desired address (hit/miss), plus the time to generate a write strobe (or enable), plus the time for which the write strobe must exist. As shown in Fig. 6, this requires a minimum write cycle time of 144 ns, assuming proper clock edges and no skew. Fig. 7 shows the cache structure used in the A900. Note the parallel nature of the logical-to-physical translation, tag store access, and data store access. The ideal minimum cycle time for this structure is 79 ns. This fits nicely in a 133-ns cycle with plenty of room for obtaining necessary clock edges and allowing for skew. This scheme for handling writes allows the A900

| 3 115  | Logical Address valid           |

|--------|---------------------------------|

| 20 ns  | Logical to Physical Translation |

| 45 ns  | Tag Store Access                |

| 20 ns  | Tag Compare                     |

| 10 ns  | Write Strobe Generation         |

| 40 ns  | Write Strobe Width              |

| 144 ns |                                 |

|        |                                 |

Fig. 6. In a normal cache memory like this one, a cache write cycle cannot begin until the appropriate address is known to be in the cache. The minimum write cycle time shown assumes proper clock edges and no skew.

1

Fig. 7. The A900 cache memory has a parallel structure, allowing faster operation than a normal cache. The minimum write cycle time fits nicely into the 133-ns cycle with plenty of time for obtaining necessary clock edges and allowing for skew.

cache to do a write every cycle and still have a very short cache cycle time.

In a typical cache memory system, direct memory access (DMA) from I/O cards comes directly into main memory. This means that main memory has to be double-ported, that is, it has to arbitrate between two address/data sources before starting the memory cycle. In the A900, DMA comes directly into the cache. This eases the problem of cache data consistency (i.e., keeping cache data and main memory data for the same address consistent). It also keeps the memory system simpler since main memory can now be single-ported. Another benefit is that it allows very tight coupling of the cache and main memory. On the A900, every access to the cache also causes the translated physical address to be sent directly to main memory. Since there is no arbitration, this address can be set up on the memory RAMs on the memory array cards. If a fault\* is detected, almost no time is lost in starting the main memory access. This gives an unusually fast fault handling cycle. Instead of the typical 6 to 12 clocks, the A900 can handle a fault in only three additional cycles. Since the effective access time of a cache memory system is described by the equation:

Effective access time = Hit cycle time × hit ratio + fault cycle time × miss ratio

decreasing the fault handling cycle can be just as effective as increasing the hit ratio, which requires the expense of a larger cache.

In addition, improving the fault handling time vastly improves system performance during periods when caches are not very effective. A typical example is process switch-

<sup>\*</sup>In this section, a fault means a miss, that is, the requested data is not in the cache and must be obtained from main memory. This kind of fault is not a memory error or failure, and the handling of this kind of fault should not be confused with memory error detection and correction.

ing, which occurs whenever an interrupt occurs. Thus, optimizing the A900's fault handling time improves its real-time capabilities.

To achieve its excellent fault handling time, the A900 uses a 32-bit path to and from main memory. Since the cache block size is 32 bits, a fault can be handled in just one read or write to main memory. This is an important feature in reducing the fault handling cycle time, thus giving more time to the processor.

#### Technology

To build a high-performance computer with a very low price, one needs not only to be clever in the design of the computer, but also to incorporate new technologies. In the design of the A900, several new technologies are used. Most of the logic in the computer uses a new fast, lowpower Schottky logic family that not only provides a fast cycle time, but does so without the added heat, power supply, and cost penalities of conventional high-speed Schottky logic.

Programmable logic arrays (PLAs) are also heavily used in the A900. Small, 20-pin versions became available just in time for use on the A900. These PLAs allow most of the state machines and decoding logic to be integrated into a very small number of devices that are very easy to alter. Most of the other random logic also uses PLAs. This made the debugging of the A900 much faster than conventional designs, so the computer could be shipped much sooner.

As mentioned earlier, the floating-point operations in the A900 are done by a set of SOS (silicon on sapphire) LSI chips. By integrating the performance-sensitive part of the computer on very low-power LSI chips, the A900's power, size, and cost were minimized while achieving a very high level of performance.

#### **Pipelining and User Microprogramming**

The A900 is the first HP 1000 Computer to use pipelining in its data path to improve performance. Pipelining affects the way in which algorithms and microcode sequences are designed. A user writing an isolated line of microcode does not need to know when the different sections of the microcode line will be executed. However, in a complete microprogram, various effects of the pipelining will show up in the register transactions, conditional status checks, memory operations, etc.

All of the microprogramming examples shown here are written in the A900 microprogramming language and can be compiled to executable microcode using the A900 microparaphraser. The A900 microprogramming language looks very much like a higher-level language using freefield notation and formats. It allows the user to generate microcode without concern for the actual format of a microword. With the microparaphraser and its associated tools in the A900 microprogramming package, a programmer can quickly generate a microprogram to enhance the performance of an application with a minimum of effort. Performance enhancements of 3 to 20 times are typical.

The pipelining of the micromachine data path has the largest impact on user microprogramming, essentially causing all micromachine data transactions to take two cycles to complete. As shown in Fig. 4, two pipeline registers, LREG and RREG, are placed in the data path at the inputs of the ALU to split data path operations into two phases.

In the first phase, data flows from the dual-ported register file (or other inputs) and is clocked into LREG and RREG. In the second phase, data is taken from the pipeline registers, flows through the ALU, and is finally stored back into the register file or other write-only registers.

The effect on user microcode is that registers stored on one cycle are not updated until two microcycles later. As a result, the microinstruction sequence

| r5:=r3; | * Microcycle 1. Copy r3 to r5.     |  |  |

|---------|------------------------------------|--|--|

| r3:=r5; | * Microcycle 2. Copy old r5 to r3. |  |  |

will swap the contents of registers r3 and r5 instead of simply copying r3 to r5 as one might expect. To have the above code sequence copy r3 to r5 you would have to add a dead cycle to allow the pipe to empty and have r5 really reflect the value of r3 before copying it back. The microinstruction sequence below will end with r5 containing the same value as r3.

| r5:=r3; | *Microcycle 1. copy r3 to r5.         |

|---------|---------------------------------------|

| nop;    | *Microcycle 2. This is a dead         |

|         | *cycle to allow r5 to get the updated |

|         | *value of r3.                         |

| r3:=r5; | *Microcycle 3. This does nothing      |

|         | *important since r5 already           |

|         | *contains the same value as r3.       |

Two special registers do exist in the A900 micromachine (the accumulators) that will reflect updated values on the very next microcycle after they are stored to. These registers are used when data must be chained through several ALU operations.

Because of data path pipelining, condition codes based on the output of the ALU will not become valid for two cycles. The microcode sequence below shows an example of testing a condition generated by the ALU.

| nop:=0;                | *Microcycle 1. Send 0 through the   |  |  |

|------------------------|-------------------------------------|--|--|

|                        | *ALU to test it.                    |  |  |

| nop;                   | *Microcycle 2. We must wait a cycle |  |  |

|                        | *for conditions from the ALU to     |  |  |

|                        | *become valid. Normally, an algo-   |  |  |

|                        | *rithm would be designed in such a  |  |  |

|                        | *way that the micromachine will be  |  |  |

|                        | *performing some other task here.   |  |  |

| If TZ then go to Zero; | *Microcycle 3. This is a test for   |  |  |

|                        | *a zero output from the ALU.        |  |  |

|                        | *TZ tests for zero so this          |  |  |

|                        | *line will jump.                    |  |  |

|                        |                                     |  |  |

Other sections of the A900 micromachine are pipelined besides the data path. One of these areas is the memory address creation logic, which is essentially another data path. Because the memory address creation logic is pipelined, microorders that work with this logic affect either the current or the following instruction. Actions can be initiated on one microcycle and then modified on the next microcycle. An example of using these microorders is shown by the following sequence. m1 < = m1 + 1;

ninc;

\*Microcycle 1. Increment memory \*address pointer m1. \*Microcycle 2. Stop the increment-\*ing of address register m1. \*Register m1 will remain \*unchanged.

Another feature of the A900 micromachine that is valuable for making algorithms execute efficiently is the ability to store data path outputs to multiple destinations at once. Dual microstore fields let the programmer create an expression such as:

m1 << r5:= r4 + 1;

\*Increment register \*r4 and store it to \*both r5 and memory \*address pointer m1.

Algorithms designed for a pipelined machine must be designed carefully to make use of every micromachine cycle. Algorithms are most efficient if they can be broken down into different sets of interdependent steps. When writing the code, these sets can be combined and intertwined so that the dependent steps of each process are separated by the number of steps in the pipe, in this case two cycles. In the A900 micromachine, dependent steps in a process can also be performed one after another by using special registers (accumulators) that bypass the data path pipe.

An algorithm that contains many decision points or conditional branches is more difficult to design efficiently on a pipelined machine. For these algorithms, operations that take more than one cycle to complete because of the pipe (such as condition code generation) should be ordered in such a way that they are meaningful if either path of an intervening conditional branch is taken. A feature of the A900 micromachine that lends itself well to designing this type of code efficiently is the ability to start a piped operation in one microcycle, and then modify its action in the next cycle before it completes. The short code sequence

If TZ then go to dont\_inc,  $m1 \le m1 + 1$ ; \*Microcycle 1. This is just a \*conditional branch that \* in the same microcycle starts \*the piped operation of incrementing \*memory address pointer m1. inc: nop; \*Microcycle 2. Here is one target of the \*conditional branch. The nop here \* is to show that memory address \*pointer m1 was incremented \*since no modifying microorder \*was used here. dont\_inc: ninc; \*Microcycle 2. Here is the other \*target of the conditional \*branch. Here a \*modifying microorder is used \*to stop the incrementing \* of m1 < = m1 + 1 before\*it has completed. \*Thusm1 < = m1 + 1\*can be effectively \*used in both paths of the \*conditional branch.

below shows an example of the use of this feature.

A final key to generating efficient algorithms for a pipelined micromachine is creating efficient code for algorithms with loops. In these algorithms, the loop time is most often the determining factor in how fast the algorithm will run. Therefore, the loop itself should be designed first for efficiency, and then the entrance and exit to the loop can be added.

## Acknowledgments

The authors wish to thank Simin Boschma and Jim Finnell who contributed to the hardware design, and Tom Harms, Chuck Morgan, and John Shelton who contributed to the firmware design. Thanks also to Donna Saar, Wayne Chin, and the many other people who contributed to the magical process of taking a processor from idea to production.

# Floating-Point Chip Set Speeds Real-Time Computer Operation

by William H. McAllister and John R. Carlson

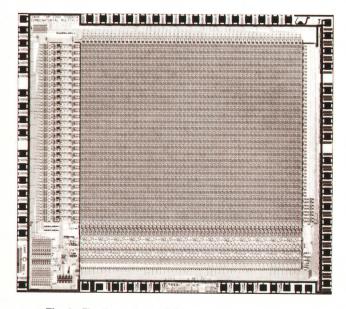

**F** LOATING-POINT ARITHMETIC performance is a prime concern in technically oriented computers. Using Hewlett-Packard's silicon-on-sapphire CMOS process we have designed a set of three monolithic floatingpoint processor chips for use in two HP 1000 A-Series Computers, the A900 and the A700. The chip set provides a cost-effective, high-performance solution for high-speed

computation.

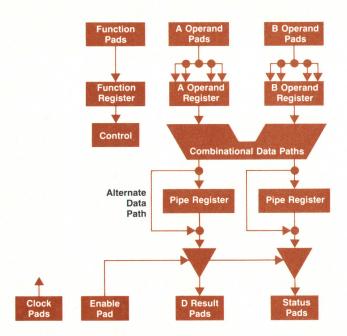

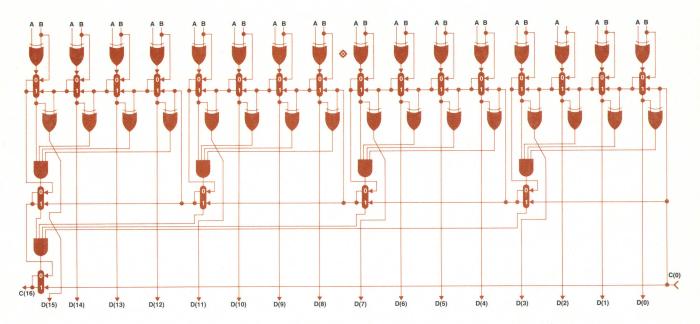

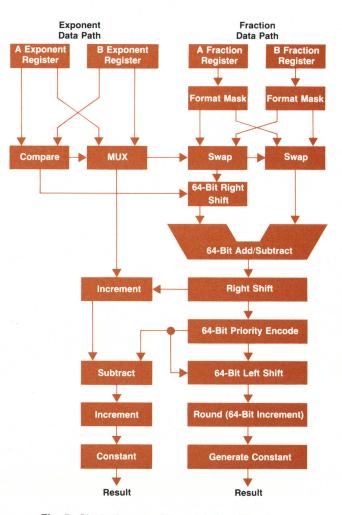

The set consists of three chips, one each for addition, multiplication, and division. Each chip can perform arithmetic operations on 32-bit and 64-bit floating-point numbers and on 32-bit integers.

The primary design objective was to maximize the speed of floating-point scalar (single-element) operations. This

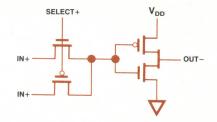

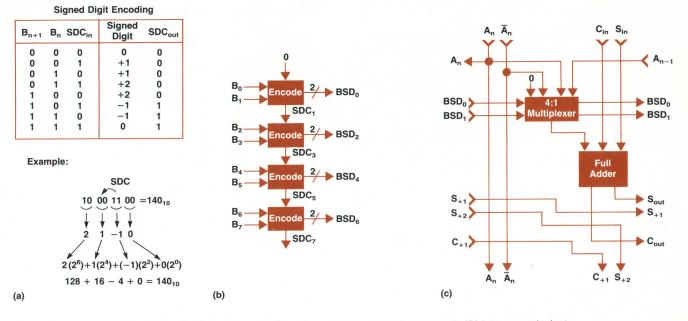

**Fig. 1.** The floating-point add, multiply, and divide chips have this block diagram in common. They have similar user interfaces and operate in roughly the same manner.

goal was achieved by partitioning the design into three integrated circuits. Each is individually optimized to provide the maximum speed for the most common floatingpoint operations. To simplify the design task and to take advantage of the inherent speed of the SOS process, we use predominantly nonclocked combinational circuits. This design technique allows each operation to proceed as quickly as the logic will allow without requiring a periodic